Lynx Software Technologies was invited, along with Mercury Systems (a partner), to participate in a webinar sponsored by Intel that focused on harnessing multicore processors for use in mission critical avionics platforms.

During the webinar, Intel announced they were licensing a Flight Safety Evidence Package for the Intel C3708 processor (I still have to use the brand names though….this is Denverton!). This package was developed to support Lockheed Martin’s certification efforts for the F-35 joint strike fighter and have been one of the primary programs that has generated a great working relationship over the last few years between the two companies. A great Intel Solution Brief is located here if you need additional information.

Multicore processors are becoming more popular to reduce size, cost, and power of platforms. One pretty recent example that is public I can reference that points the way is from Army Aviation. The AMCS program has the objective to deploy a “cloud server in the sky”.

This directly highlights digital convergence and the demand for increased performance in mission critical applications. Based on the published articles, the Army’s objectives are to converge applications into an Airborne Common Server, leveraging MOSAs (Modular Open Systems Approach) such as OpenVPX and SOSA profiles to provide a more affordable, agile, and adaptable system. Achieving the goal of supporting this on a platform is going to require significant processing performance improvements (maybe 20- 50x) over legacy processors.

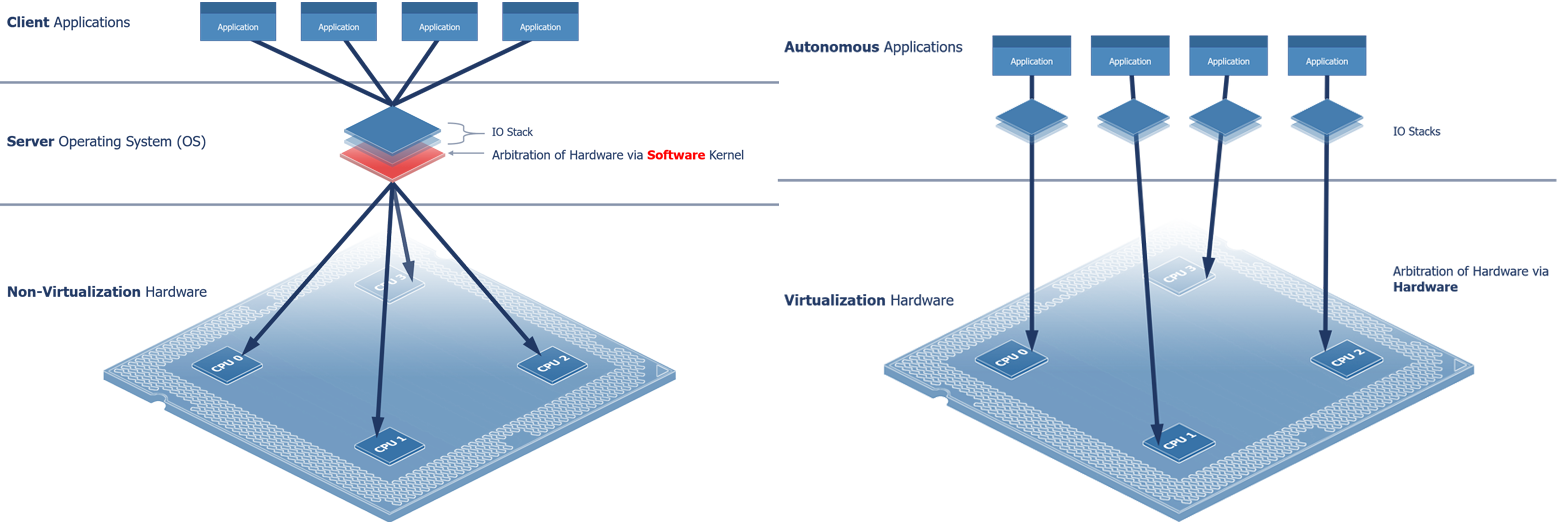

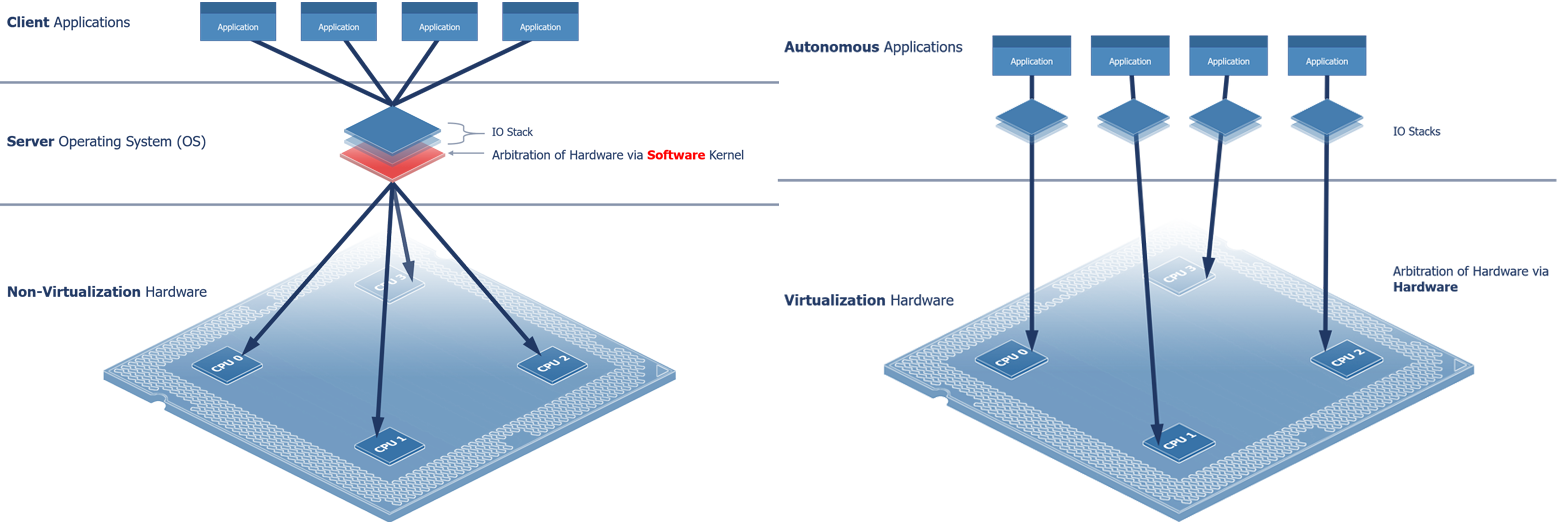

There are numerous challenges in building safe systems on multicore processors. Current multicore processors exhibit non-deterministic memory access delays when competing for shared resources. When multiple applications stacks run in parallel on multicore processors, interference occurs. Interference can be caused from both hardware and software level contention.

Examples of identified interference channels with their impact include:

- Unpredictable hit/miss response times from every shared-cache, due to competition across cores

- Unpredictable miss latency and core stall durations due to flooding of cache miss buffers

- Unpredictable latency due to cores’ competitions for memory controllers’ transaction queue/ arbiter hardware resources

- Unpredictable latency within DRAM devices, especially due to memory transaction re-ordering and other intractable problems that arise due to the mismatch between where data is stored vs. the sequence of memory transactions that arrive at DRAM devices in real-time

The industry is aware of the impact of multicore interference channels, led by the avionics industry, and increasingly the automotive industry. Companies like Intel are adding functionality to ease the challenge and this webinar started to touch of some of those aspects, including Intel Resource Director Technology.

Of course, this needs to be complemented with software technology that can help with fine grained allocation of hardware resources to specific virtual machines and strongly isolate applications from each other to improve the immunity of the system to single point failures and malicious/intentional system attacks.

Lynx’s delivery for the Denverton processor includes LYNX MOSA.ic (that name is not a coincidence – it was designed to deliver MOSA) which consists of a separation kernel hypervisor, LynxSecure, that fully harnesses the component’s multicore support, virtualization, cache partitioning, and SR-IOV virtual network device functionality.

The LynxOS-178 operating system provides API support for POSIX, FACE and ARINC 653 and includes pre-certified software components to simplify the path to system certification. The journey starts here. We are committed to delivering software to support a diverse range of Intel’s future processors including ElkHart Lake and Intel’s 11th generation Core processor, Tiger Lake.

To listen in to the recording of the webinar, simply register here. You can also explore our Learning Center, where we cover topics such as The Benefits of POSIX, Challenges Building Safe Multicore Systems, and How to Choose an RTOS.

Ian Ferguson | VP Marketing

Ian Ferguson | VP Marketing