TECHNICAL ARTICLES

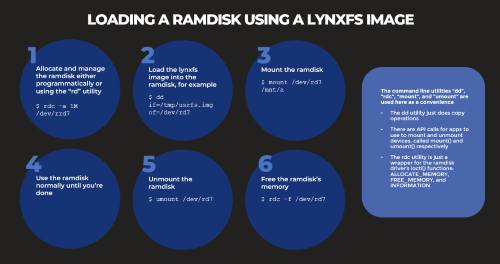

Using and Sharing RAM Disks in LYNXOS-178

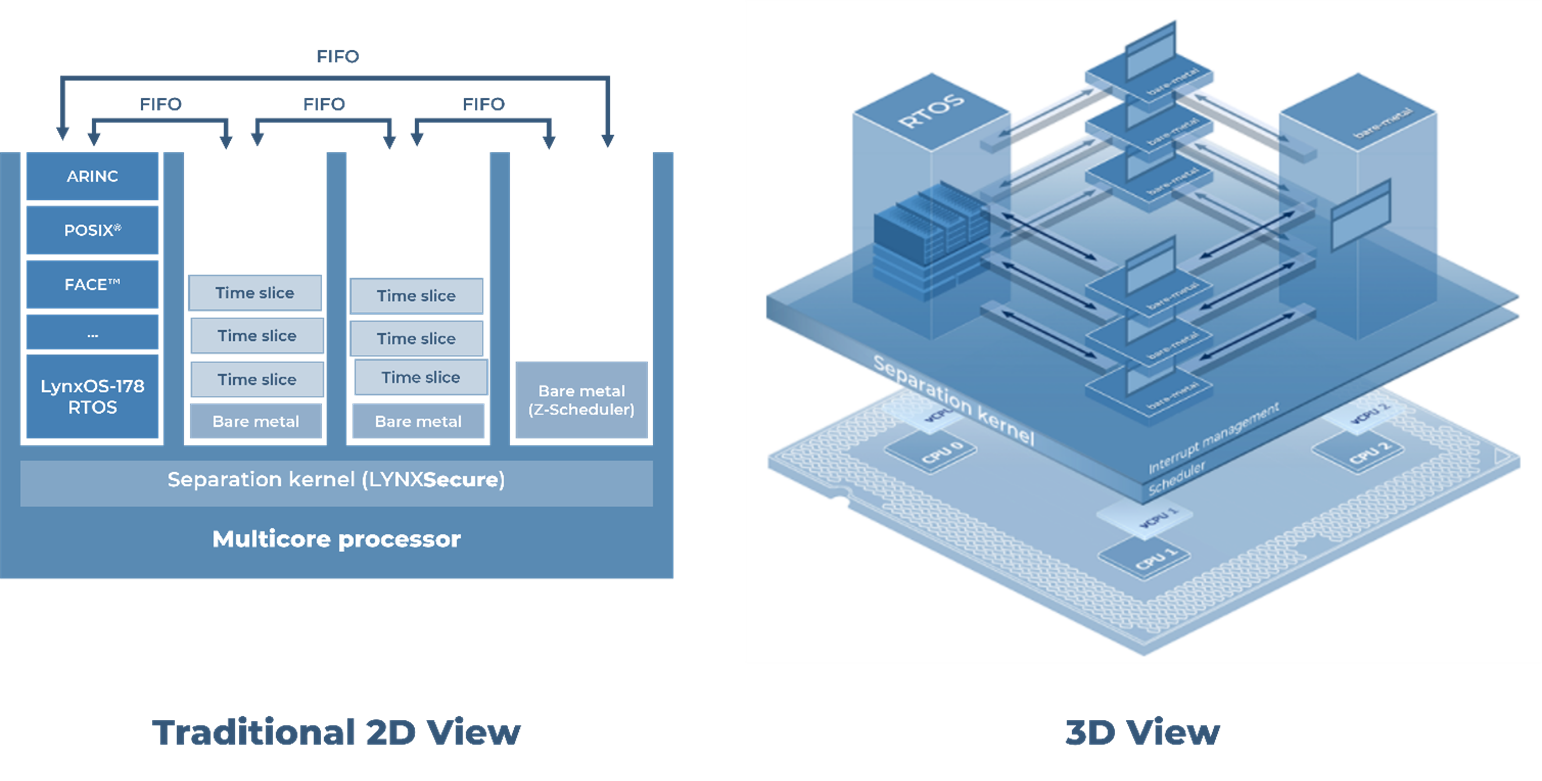

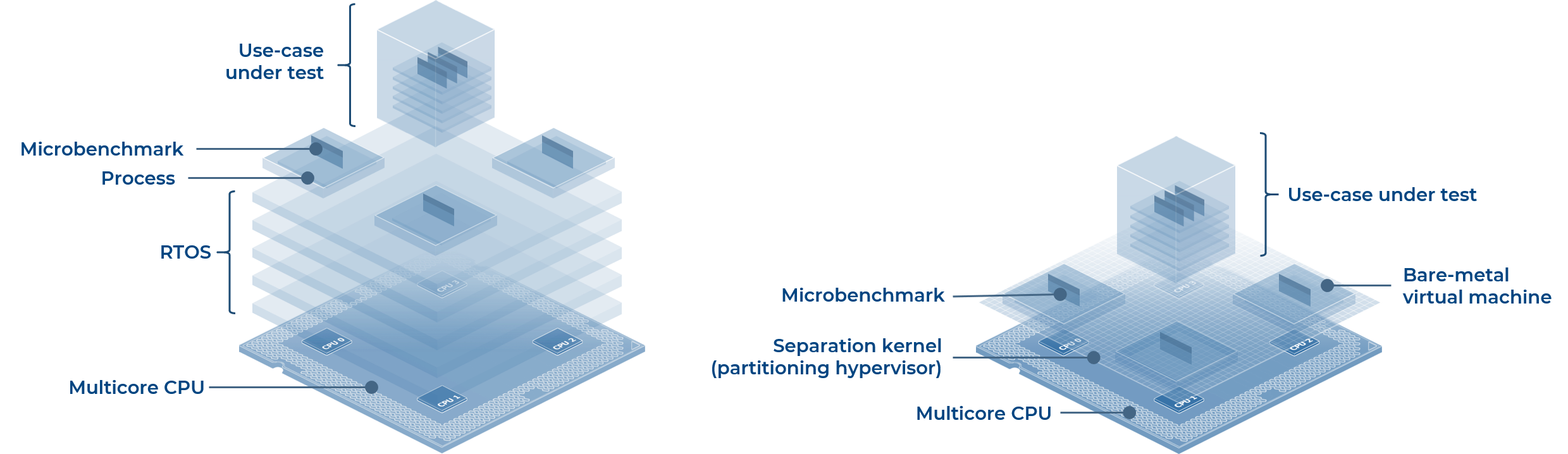

IMPORTANCE OF SYSTEM ARCHITECTURE AND PLATFORM CHOICE ON SAFETY CERTIFICATION

Introducing the Z-Application-Bridging the gap between bare metal and rtos

Single Root I/O Virtualization (SR-IOV) -Pt 2- LynxOS-178 10G network benchmarkS

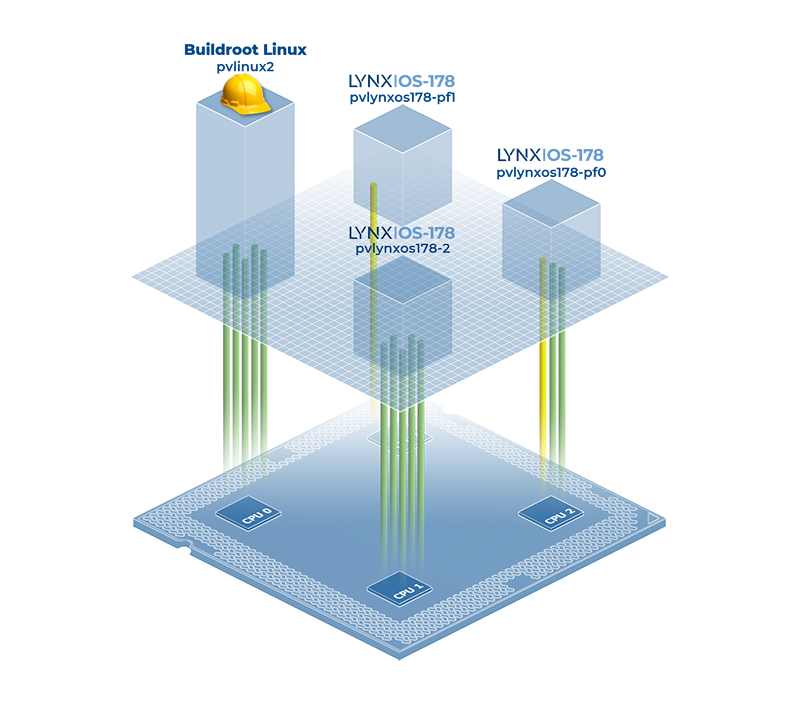

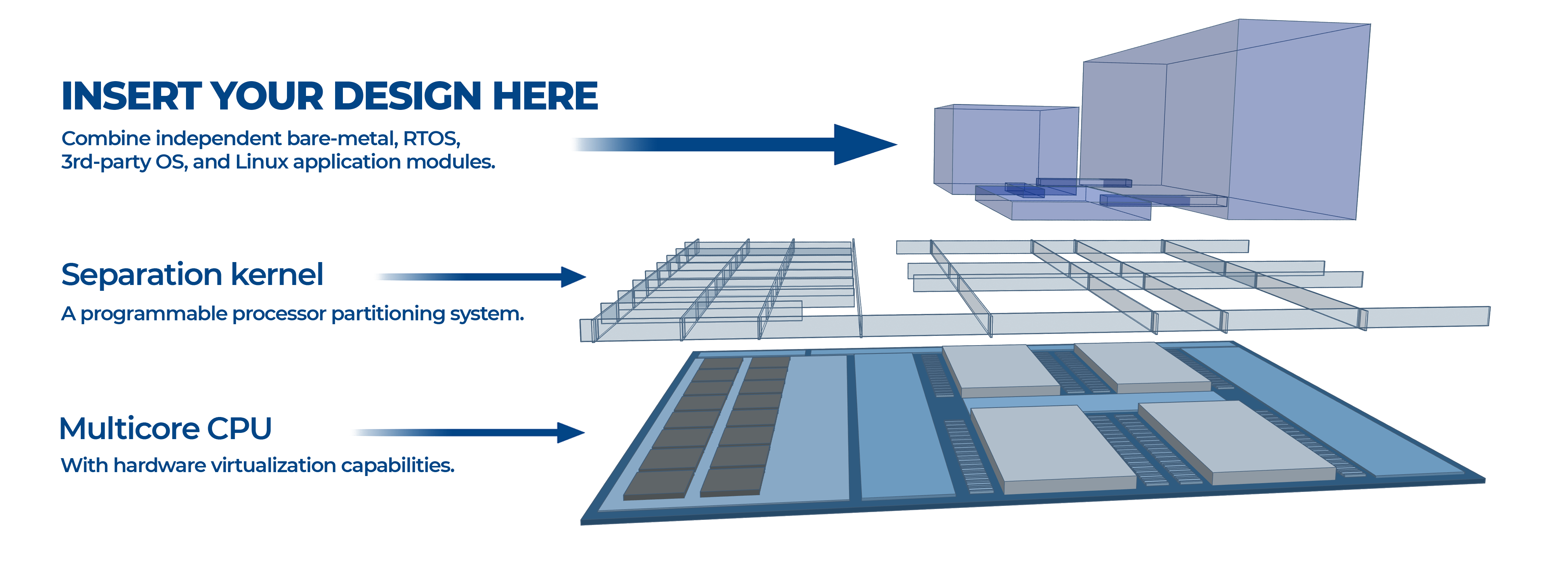

Who Needs a Hypervisor?

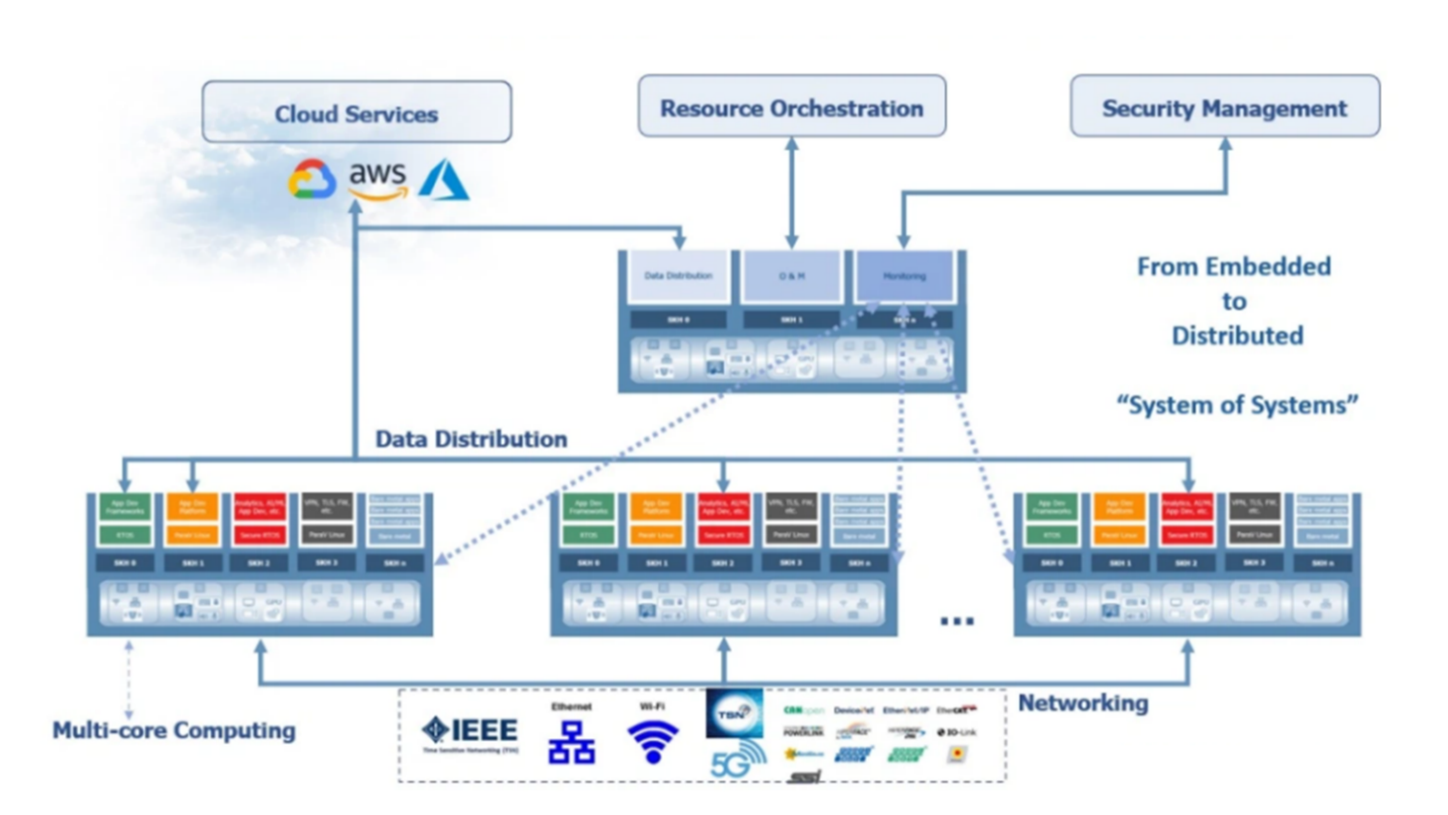

Edge Computing is Here. What's Next?

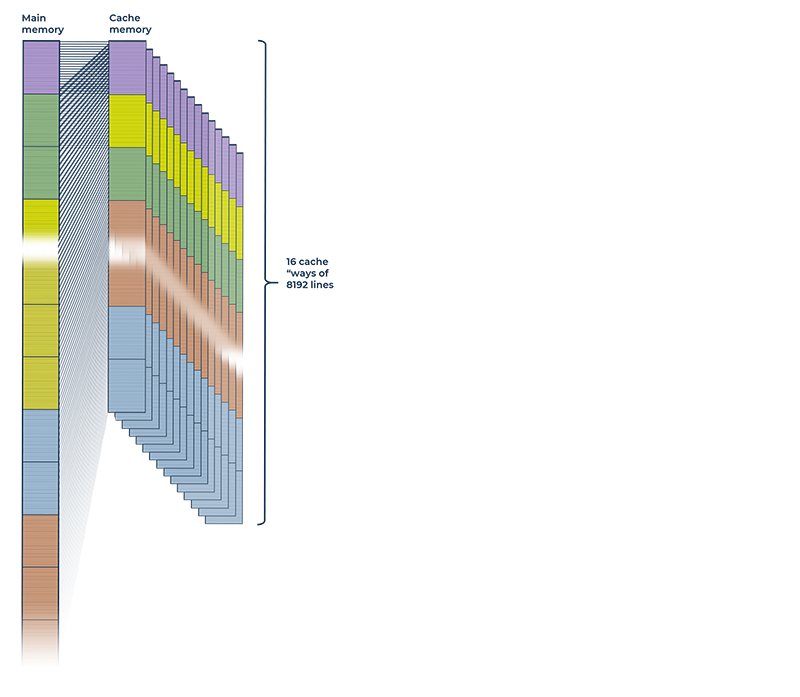

What is Cache Coloring and How Does it Work?

On reference architectures